当社は、これまでイメージセンサー、カメラモジュールを用いた産業機器製品の開発を多く対応してきました。

この経験を活かし イメージセンサー向けインターフェース規格である SVLS-ECインターフェースの受信モジュール "SLVS-EC RX" を開発しました。

SLVS-ECについて

SLVS-EC(Scalable Low Voltage Signaling with Embedded Clock)は、イメージセンサー向けの高速インターフェース規格です。

エンベデッドクロック方式を採用しているため、データとクロック間のスキューを調整する必要がなく、高速・長距離伝送が求められるアプリケー ションに最適です。

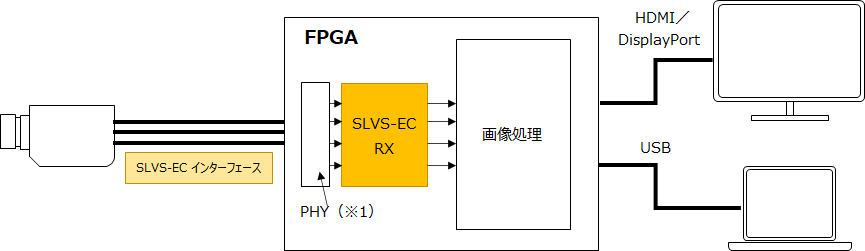

概要

SLVS-ECインターフェース受信モジュール "SLVS-EC RX"は、SLVS-EC信号をFPGAの高速トランシーバーを経由して受信したバイトデータから、画像情報及び画像データの デコード処理を行い出力します。

主な仕様

SLVS-EC RXの主な仕様は次の通りです。

| SLVS-EC インターフェース規格 | Version2.0 に準拠 |

| Baud Grade | Grade1,Grade2,Grade3に対応 |

| Pixelデータ | 8bit,10bit,12bit,14bit,16bitに対応 |

| Lane数 | 1Lane,2Lane,4Lane,8Laneに対応 |

| CRC機能 | 対応(On/Off 切り替え可) |

| ECC機能 | 非対応 |

| マルチストリーム | 非対応 |

リソース使用量

リソース使用量の参考値を下記に示します。

| AMD-Xilinx社 Zynq UltraScale+ | Intel社 Arria10シリーズ | |

| レジスタ | 4407 | 4624 |

| LUT | 4161 | 2900 |

| RAM | 0 | 0 |

SLVS-EC RX は、RAMを使用せず、かつ、レジスタ、LUT使用量も少ないという特長があります。

画像処理には多くのRAMやロジックが必要になるので、SLVS-EC RX のリソース使用量が少ない分、空いたリソースをシステムの主機能に使用していただくことが可能です。

評価・デモ

当社では、2020年に、製品設計の品質向上を目的とした社内プロジェクト 「ASTRA」を発足しました。

ASTRAプロジェクトで開発済のASTRAボードに、SLVS-EC RX を搭載し CMOSイメージセンサーを接続。 イメージセンサーからデータを受信し、画像処理を施し、モニタへ表示する システムを構築し、実機評価も実施しています。