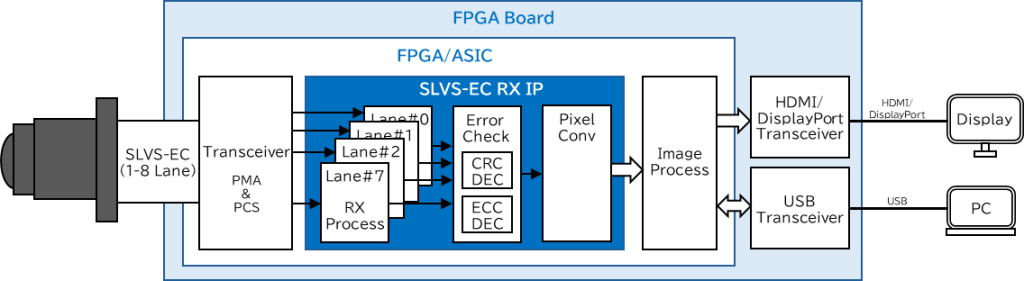

SLVS-EC(Scalable Low Voltage Signaling with Embedded Clock)は、イメージセンサー向けの高速インターフェース規格です。エンベデッドクロック方式を採用しているため、データとクロック間のスキューを調整する必要がなく、高速・長距離伝送が求められるアプリケーションに最適です。

SLVS-ECインターフェース受信IP “SLVS-EC RX IP“ は、SLVS-EC信号をFPGAの高速トランシーバーを経由して受信したバイトデータから、画像情報及び画像データのデコードして出力します。RAM、ROM、PLLなどを使用せず、Verilog-HDL構文のみで設計されています。そのため、SLVS-EC RX IPは様々なFPGAデバイスに適用可能な上、レジスタやLUTの使用量も少ない特長があります。画像処理には多くのRAMやロジックが必要ですが、SLVS-EC RXのリソース使用量が少ないため、空きリソースをシステムの主機能に活用することが可能となります。

特徴

- SLVS-EC Specification:v2.0準拠

- Baud Grade:1、2、3 (最大 5Gbps)

- Pixel Data:8、10、12、14、16bit

- Number of Lanes:1、2、4、8

- CRC:対応 (On/Off切替可)

- ECC:オプション

- Multiple Stream:非対応

対応デバイス

- AMD UltraScale+ (Zynq,Vertex,Kintex,Artix)

UltraScale (Vertex,Kintex)

- Altera Arria (10 Series,V Series)※

Cyclone (10 Series,V Series)※

- Microchip PolarFire ※

- Lattice CertusPro-NX

その他のデバイスは、現在、検証継続中

※ 複数レーン使用時にトランシーバーがレーン間のデスキューができない場合は、トランシーバーとSLVS-EC RX IPの間にデスキュー回路が必要です。(当社でも提供可能)

リソース使用量

8Lane構成時 (高速トランシーバー含まず)

| AMD UltraScale+ | Altera Arria10 | |

| Register | 4407 | 4624 |

| LUT | 4161 | 2900 |

| RAM | 0 | 0 |

入出力信号一覧

| 信号名 | I/O | Bit幅 | 説 明 |

| RESET N | IN | 1 | 非同期リセット |

| CLK | IN | 1 | クロック |

| I_DT0_0~3 | IN | 4×8 | レーン0 1st~4th バイトデータ |

| I_DT1_0~3 | IN | 4×8 | レーン1 1st~4th バイトデータ |

| I_DT2_0~3 | IN | 4×8 | レーン2 1st~4th バイトデータ |

| I_DT3_0~3 | IN | 4×8 | レーン3 1st~4th バイトデータ |

| I_DT4_0~3 | IN | 4×8 | レーン4 1st~4th バイトデータ |

| I_DT5_0~3 | IN | 4×8 | レーン5 1st~4th バイトデータ |

| I_DT6_0~3 | IN | 4×8 | レーン6 1st~4th バイトデータ |

| I_DT7_0~3 | IN | 4×8 | レーン7 1st~4th バイトデータ |

| I_KC0_0~3 | IN | 4 | レーン0 1st~4th データ制御シンボル検出フラグ |

| I_KC1_0~3 | IN | 4 | レーン1 1st~4th データ制御シンボル検出フラグ |

| I_KC2_0~3 | IN | 4 | レーン2 1st~4th データ制御シンボル検出フラグ |

| I_KC3_0~3 | IN | 4 | レーン3 1st~4th データ制御シンボル検出フラグ |

| I_KC4_0~3 | IN | 4 | レーン4 1st~4th データ制御シンボル検出フラグ |

| I_KC5_0~3 | IN | 4 | レーン5 1st~4th データ制御シンボル検出フラグ |

| I_KC6_0~3 | IN | 4 | レーン6 1st~4th データ制御シンボル検出フラグ |

| I_KC7_0~3 | IN | 4 | レーン7 1st~4th データ制御シンボル検出フラグ |

| 0_FRAME_START | OUT | 1 | フレーム開始信号 |

| 0_FRAME_END | OUT | 1 | フレーム終了信号 |

| 0_EMB_LINE | OUT | 1 | エンベデッドライン信号 |

| 0_LINE_VALID | OUT | 1 | ライン有効信号 |

| 0_LINE_NUM | OUT | 13 | ライン番号 |

| 0_DATA_ID | OUT | 4 | データID |

| 0_HDCRC_ERR | OUT | 1 | ヘッダーCRCエラー出力 |

| 0_HD_INFO | OUT | 48 | パケットのヘッダー信号出力 |

| 0_LINE_EN | OUT | 1 | パケット(ライン) 出力有効信号 |

| 0_DT_EN | OUT | 1 | パケット(ライン) データ出力有効信号 |

| 0_SOL | OUT | 1 | パケット(ライン) 開始信号 |

| 0_EOL | OUT | 1 | パケット(ライン) 終了信号 |

| 0_DT_0~31 | OUT | 16×32 | ピクセルデータ 0~31 |

| 0_CRC_ERR | OUT | 16 | ペイロードCRCエラー出力 |

実機評価

SLVS-EC RX IPを自社開発ボードに組み込み、CMOSイメージセンサーからのデータを処理してディスプレイに表示するシステム(製品評価)を構築しています。

提供物

- 暗号化RTL (Verilog-HDL)※

- シミュレーション環境 (ModelSim or VCS)

- ユーザーガイド

※暗号化は各 FPGA ベンダーのコンパイラによって実行されるため、FPGA ベンダー毎に個別に提供されます。

SLVS-EC RX IP販売及び、搭載したFPGA/ASIC、ボード開発も承ります。

お気軽にお問い合わせください。